Preface. Computer chip fabrication plants need to run continuously for weeks to accomplish the thousands of steps needed to make microchips. A half-hour power outage at Samsung’s Pyeongtaek chip plant caused losses of over $43 million dollars (Reuters 2019).

Chip production requires massive amounts of water, but reservoirs in Taiwan are critically low and authorities have already cut supplies to agriculture to support industrial and residential use. Taiwan’s tech manufacturers fear their output is under threat from the island’s worst drought in decades, risking more turmoil for global supply chains already strained by shortages of semiconductors and other key components (Ting-Fang and Li 2021).

An electric grid depending on intermittent power like wind and solar will be up and down too much to make chips, which takes hundreds of steps over several days. If a grid can come up and down that is — blackstarting is not easy and outages can damage transformers.

As oil declines, at some point the energy to mine the materials and to make the precision machines that make the chips, chemicals, etching and other machines will end. But until then, appreciate what you have a lot more!

Alex commented below about a post at here. Felix Moreno predicts that because oil peaked in 2019. peak memory and peak data will arrive in 2021, or optimistically as late as 2024. If true there’ll be problems storing data and at some point society will lose the ability to hold onto archived files, starting with individuals but that will affect governments and companies. And much more…

Alice Friedemann www.energyskeptic.com author of “When Trucks Stop Running: Energy and the Future of Transportation”, 2015, Springer, Barriers to Making Algal Biofuels, and “Crunch! Whole Grain Artisan Chips and Crackers”. Podcasts: Collapse Chronicles, Derrick Jensen, Practical Prepping, KunstlerCast 253, KunstlerCast278, Peak Prosperity , XX2 report

***

The crowning achievement of our civilization is the ability to make microchips. It is by far the most complex object ever made by mankind. Probably second in complexity to the microchip is the $10 billion dollar clean room they’re made within. And third, the motherboard inside computers. Everything else pales in comparison. Nearly any electronic device you can think of depends on a microchip to function. Even toasters. Somewhere along the line, even complex objects that don’t have one, like batteries, were made with equipment that used chips.

Enormously expensive

Moore’s Law says that over the history of computing hardware, the number of transistors in a dense integrated circuit doubles approximately every two years. Some say that Moore’s 2nd Law is the escalating cost of a semiconductor fab plant, which doubles every 3 years. For example, Intel’s Fab 32 cost an estimated $3 billion in 2007, revised to $3.5 billion in 2011. A 2009-2010 upgrade to an Intel fab, Fab 11X, cost $2.5 billion (on top of a 2007 $2 billion upgrade). The first stage of GlobalFoundries’ New York 1.3 million square foot fab will cost >$4.6 billion dollars. TSMC’s Fab 15 in Taiwan is estimated at >$9.3 billion, and they are preparing to start a fab in 2015 projected at >$26 billion.

Only 5 companies can afford to make the best microprocessors: a supply chain threat

The costs and risks involved in building new fabs have already driven many makers of logic chips (processor or controller chips) towards a “fabless” chip model, where they outsource much of their production to chip “foundries” in the Far East (Nuttall).

High capital costs require fabs to keep their production lines running at full capacity to pay back the money sunk into them. “The most expensive thing on the planet is a half-empty fab,” says Brian Krzanich, general manager of Intel’s manufacturing and supply chain. Consequently, only the highest-volume processor manufacturers–such as Samsung and Intel are still sole owners and operators of state-of-the-art plants. As the elements on a chip become smaller, designing processors is getting tougher costing a lot more — R&D costs are rapidly increasing. In 2009, around $30 billion, or 17 percent of revenue, went to R&D across the industry–a 40 percent increase over 1999 (Mims).

Back when 130 nm chips were made, there were 20 companies, but now there are only 5 companies making the cutting edge 20/22 nm. Below you can see the declining number of companies as the size got smaller and cost significantly more to make (Benini):

- 20/22 nm: Globalfoundries, Intel, Samsung, ST Microelectronics, TSMC

- 28/32 nm: 20/22 and Panasonic, UMC

- 40/45 nm: 20/22, 28/32, and Fujitsu, IBM, Renesas (NEC), SMIC, Toshiba

- 55/65 nm: 20/22, 28/32, 40/45 and Freescale, Infineon, Sony, Texas Instruments

- 90 nm: 20/22, 28/32, 40/45, 55/65 and Dongbu Hitek, Grace Semiconductor, Seiko Epson

- 130 nm: 20/22, 28/32, 40/45, 55/65, 90 nm and Altis Semiconductor

Only 3 companies still make internal hard disk drives

Seagate Technology, Toshiba, and Western Digital. Once there were 200 companies.

One company, ASML, makes most of the lithography equipment for the semiconductor industry

ASML is a lithography equipment manufacturer for the semiconductor industry, without which chip manufacturers cannot make computer chips for the computer and telecom industries. ASML is nearly a monopoly company in the semiconductor lithography market with 74% of the market share. Traditional lithography has reached the limits and smaller chips can only be made using extreme ultraviolet lithography [EUV]. ASML enjoys a monopolistic position in EUV as it is the only company that is developing EUV equipment to produce these smaller computer chips. The capital required is so huge that ASML’s main customers such as Intel (INTC) are participating in a customer co-investment program (SeekingAlpha).

Benini says that Moore’s Law is about to hit a brick wall because of:

- Market volume wall: only the largest volume products will be manufactured with the most advanced technology (above)

- Thermal wall: transistor count still increases exponentially but we can no longer power the entire chip (voltages, cooling do not scale)

- Memory wall: larger data sets and limited bandwidth at high power cost for accessing external memory

Financial fragility

In a (civil) war, fabrication plants are a likely target. Given how expensive they are, could a company survive the destruction of one or two of their plants given that their revenues now are often less than the cost of building a new fab plant (i.e. TSMC $14 billion, Globalfoundry $3.5 billion)?

Overview of how Chips are made

The main steps are oxidation layering, photoresist coating, patterning, etching, layering, doping (diffusion and ion implantation), depositing interconnection metals, testing, and packaging. Each step can have dozens to hundreds of steps, with every process requiring astonishingly pure air, water, and chemicals. Even the tiniest particle can contaminate the wafer and the microchip will have to be thrown out.

The fabrication building semiconductors are made in is also amazing. It’s made of materials that shed as few particles as possible, and the flooring and machinery must be built to prevent even the slightest vibrations from a truck going by or the chips will be damaged. Temperatures and humidity must stay within very narrow limits.

There are hundreds of thousands of kinds of equipment, chemicals, metals, minerals, and complex heating, cooling, building systems. All of them are potential victims of supply chain failures.

As the world becomes less complex on the down-slope of the fossil fuel energy curve, it will get harder to keep the air, water, chemicals, and silicone as pure as they are now. The more impurities or particles there are, the more chips will fail at the end-of-the-line. I personally experienced these frustrations when I worked at a neuroanatomy lab in Puerto Rico that moved from Urbana, Illinois. Suddenly we couldn’t get histology to work. The water and air weren’t pure enough, and this was worsened by not being able to come and go all hours of the day and night since the area was so unsafe.

At this point there are enough facilities and suppliers in about 9 countries that can back each other up after earthquakes (Taiwan & Japan), tsunamis (Japan), floods (Thailand), and other natural disasters, lessening supply chain worries.

But this is changing. According to Quartz, only four companies, Intel, Samsung, Taiwan Semiconductor Manufacturing (TSMC), and GlobalFoundries, are able to make advanced microchips. In the relentless pursuit of Moore’s law, only a few companies remain with the money and knowledge to stay up-to-date. Smaller suppliers of the big 4 that couldn’t afford to do the research to reach the next level of complexity in EUV lithography, 3D-IC chip packages and 450mm wafers are going out of business as well.

The biggest threat to chip production in the future are world-wide financial crashes, electric grid outages, and oil shortages resulting in disruption of supply chains, which will eventually affect facilities in more and more of the countries that are still making chips.

Another world-wide threat to the production of microprocessors is (nuclear) war, and cyber war and cyber attacks. While looking for a list of devices with chips, I came across an article about how Russians detected spy chips hidden inside electric irons and electric kettles that could put malware and viruses on computers within 600 feet.

Everything depends on semiconductors. Financial and business transactions, logistics, shopping, corporations and small businesses, shipping, trucks, trains, autos, and so on. No microchips, no Civilization As We Know It.

As you can tell from my booklist, for me the greatest tragedy will be the loss of most of the knowledge gained during this short Age of Enlightenment, and then it’s back to superstition and fear of the Unknown. More and more of what we know is only being stored electronically. Librarians have written me to say their university or library is trying to put everything online. Whatever is electronic will all be lost when we’re no longer able to make semiconductors. We’ll also lose what’s on paper or microfilm since those don’t last more than a few centuries. I discuss this at greater length in Peak Resources and the Preservation of Knowledge. Carl Sagan best expresses the sadness I feel in “The Demon-Haunted World: Science as a Candle in the Dark” and anthropological works like Chagnon’s “Noble Savages”.

The physics and calculus

You really need to see the diagrams, calculus, problems, and discussions of the physics involved to truly appreciate the complexity. The list of processes below doesn’t begin to capture how amazing, brilliant, and unappreciated this enterprise is! Try scrolling a bit through one or more of these textbooks to get an inkling of what I mean:

Handbook of Semiconductor Manufacturing Technology, Second Edition

Advanced Processes for 193-nm Immersion Lithography

Handbook for Cleaning for Semiconductor Manufacturing

Fundamentals of Semiconductor Manufacturing and Process Control

Semiconductor Manufacturing Technology

Videos: From sand to chip – How a CPU is made

A Detailed Look at the process of making Microchips from an 800 page textbook

Hwaiyu Gent. Semiconductor Manufacturing Handbook. Wafer Processing Technologies. Nanotechnology and MEMs. Fab yield, operations, and facilities. 2005.

Here are just a few devices that depend on microchips: medical equipment of all kinds, manufacturing equipment, Vehicles, Cameras & Video Equipment, Cellular Phones, Copy Machines, Printers, Hearing Aids, Sewing Machines, stereos, radios, televisions, VCRs, air conditioner, thermostat, microwave, washing machine, security system, routers, ATMs, clock radios, coffee makers, ovens, etc.

Now and then I note the chemicals or minerals used in the process to give you an idea of the complexity.

A Brief description of some of Intel’s Fab facilities (Andrews)

- 400,000 square feet of cleanrooms a quarter-mile on a side.

- 40 miles of pipes for ultrapure water

- 3 miles of internal monorail transportation

- clean rooms constructed with custom pre-cleaned construction materials.

- Cement consumption is so high that Intel builds cement plants on their construction site

- Chip fab energy consumption is 55-65 megawatts in one case. I

- The largest land-based crane in the world was used to pick up and place massive roof trusses that weigh approximately 300 tons each.

- The crane is so large it had to be delivered on trucks to the site in pieces by 250 trucks

- 24,000 tons of steel rebar

- 21,000 tons of structural steel. And to make room for the fab,

- 875,000 cubic yards of dirt had excavated to make room for the fab plant

- 10.5 million man hours will be required to complete the project.

- Basic equipment can cost over $40,000,000 for a lithography machine, and over $50,000,000 for steppers

- Software. In 1995 a chip that went into a stand-alone product and required 100,000 lines of code, in 2002: a typical chip for a networked programmable product required a million lines of code (Fiddler)

How Silicon Wafers are made

Silicon wafers are the platform for microprocessors used in transistors, power and RF devices, dynamic random access memories (dram), and microprocessors. There are many ways to make them. The more complex microprocessors require much more processing and materials often layering is done with diamonds, Si-Ge, and other materials, like a complex submarine sandwich that might include gallium arsenide, indium phosphide and antimonide, Si-Ge.

Arc furnace: reduce quartz in quartzite by carbon into metallurgical grade silicon purified with halogenation and fractional distillation processes. HCl SiHCl SiCl4 H2 AlCl3 BCl3 FeCl3

Reactor: Decompose Trichloro silane into silicon and HCL. molybdenum

Quartz crucible. Within a chamber having a controlled atmosphere to grow the silicon crystals using very careful temperature control

Annealing. Wafers placed in an atmosphere of argon or hydrogen to remove oxygen, etc.

Slice: multiwire saws slice and then grinders, lapping, and polishing machines produce wafers

Interconnects/wiring systems

These provide power, grounding for various systems on the chip. Copper, TaN, TiN, TiSiN, TiW

Make interconnect (with copper): A mold is coated with liner and seed layers, then copper is electrochemically poured in, with excess removed in a polishing step, and finally the surface is capped with a dielectric material to protect the copper often with a plasma-enhanced chemical vapor deposition.

Apply Silicide: Because as devices shrink to the submicron level, circuit performance has encountered problems that can slow it down, and this is solved by applying silicides, which ideally have low resistivity, easily form thin films, withstand chemicals and high temperatures, adhere well to other layers, is smooth, and much more. titanium, cobalt, nickel, platinum, tungsten, molybdenum, tantalum and other metals. There are many possible compositions of silicides, each with their strengths and weaknesses. TiSi2 CoSi2 NiSi Pd2Si PtSi Wsi2 MoSi2

Deposit a film of metal on a silicon substrate and bind by annealing.

- sputter clean silicon wafer with Ar ions

- the metal is sputter deposited

- anneal in a 100% N2 ambient

- wet etch

- Another annealing cycle from 700 to 850 degrees C (depending on metal). Now they’re ready for contact dielectric deposition and 1st level metal-interconnect processing

Plasma process control

An intricate and central feature of making semiconductor devices. Plasma chambers etch or deposit thin films of material. Etching needs a high-density plasma that generates ions which remove atoms of material. Deposition is similar except coating is the objective.

Optical Emmission Spectroscopy(OES): uses an optical sensor(CCD image sensor and optical filter) to detect the oxide-etch endpoint and measure the spectral emission from the plasma

Dry etch process: 2 types: chemical and physical, which combine to form 4 plasma processes: sputtering or physical, chemical, ion-energy-driven, and ion-enhanced-inhibitor etching. Chemical etch is done in high-pressure conditions.

Vacuum technology: Essential in many processes that need a controlled environment to deposit thin films so that the atmospheric gas molecules don’t interfere.

Vacuum technology Measurement Equipment required: Force Displacement Gauges (liquid level barometer, U-Tube manometer, McLeod Gauge, Bourdon-tube gauge, diaphragm gauge), Capacitance Manometers, Thermal Transfer Gauges (thermocouple gauge Pirani gauge, convection-enhanced Pirani gauge), Ionization Gauges (hot cathode ionization, cold cathode ionization, Partial Pressure analyzers, Residual gas analyzers. Platinum

Vacuum creating equipment required: Primary vacuum pumps (oil sealed rotary vane mechanical, dry (diaphragm, scroll, screw, sorption pumps). Secondary vacuum pumps (momentum transfer, Oi0-pVapor diffusion, Turbomolecular, Gas Capture, Cryogenic Vacuum, Sputter Ion) liquid nitrogen, titanium, helium, neon, argon, krypton, xenon, radon

Vacuum creating components: Flanges with demountable seals to connect to vacuum vessel, valves to control the flow of gas in and out, feed-throughs allow for mechanical motion, radiation, or fluids in and out of vacuum vessels to manipulate objects inside the vacuum

Vacuum Leak Detectors: Untrasonic leak detection, Helium Mass Spectrometer leak Detector (HMSLD)

Photomasks

The intermediate steps between design and wafer, the stencils used to print images onto the semiconductor material.

Data Prep: Design data is conditioned to generate instructions for the pattern generator to use to print the mask features, then converted to a file format acceptable to the pattern generation tool. Enormous computer resources are needed for this complex step. As chips shrink, exponentially larger pattern files are required to cope. The generated files are so large that transferring them from the design center to the photomask vendor taxes networks.

Pattern Generation: The design data are printed on resist-coated photoblank with electron beam (ebeam) systems in a high vacuum that take 10 to 18 hours, or with laser-beamed systems using deep ultraviolet lasers in 5 to 9 hours. Atlas laser systems split the laser into 32 separate beams that are raster scanned across the mask with a 24-facet rotating cylindrical mirror.

Postexposure Bake: After patterning, this step removes standing waves formed from reflections of the substrate surface since these can degrade the resist image leading to poor uniformity

Develop process: The exposed resist is removed by solvents, and surfactants improve the wetting of the resist, then developers are added with puddle processes left on top for a while and then rinsed off, or sprayed on. tetramethylammonium hydroxide

Etch process: After the exposed resist is removed, the underlying chrome is etched with wet processes using powerful acids or dry etch methods that use gases such as chlorine in a plasma induced by radio frequency energy

Resist removal and cleaning: After the pattern is etched into the chrome of the photomask, unexposed resist is removed with strong acids

Inspections: Quality assurance to make sure mask features were printed at the proper size, defect inspections

Final Cleaning and pellicle mounting: Strong acids to clean, then a pellicle (rectangular anodized metal frame with optically transparent film on it) over the printable field to protect it from contamination at the wafer fabrication plant.

Final shipment: The photomask is read to be shipped to the wafer lab

Some statistics: File sizes for design data ranged from 1.5 to 76 GM. Data preparation times averaged 6.5 hours of CPU time with a max of 360 hours.

Wafer processing with Microlithography

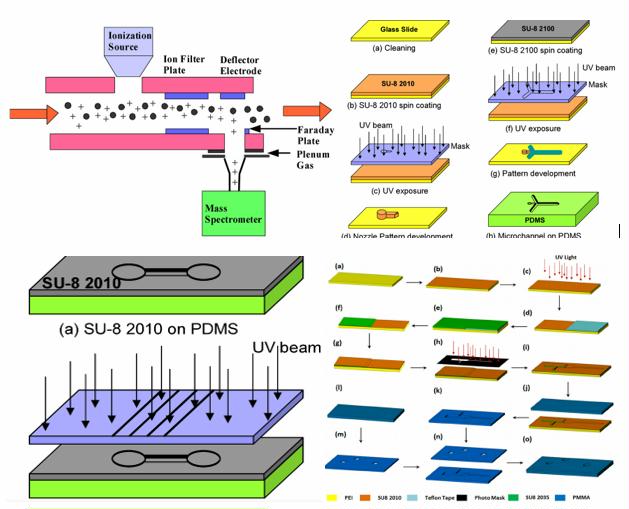

Fabrication processes of an integrated circuit fall into 3 categories: film deposition, patterning, and semiconductor doping. Conductors and insulators are used to connect and isolate transistors. Doping allows the conductivity of the silicon to vary with voltage. fundamental to all of these processes is lithography which forms 3D relief images on the substrate where the pattern can be transferred to. The patterns are written with a photoresist lithography and etch transfer step usually up to 30 times to build the millions of transistors and many wires. Each pattern printed is aligned to the previous pattern and slowly the conductors, insulators, and doped regions are built up to form the final device.

Lithography: “This accounts for about 30% of the cost of manufacturing, and it’s often the technical limitation on reducing the size of the chip even further. Optical lithography is a photographic process which exposes the photoresist (a light sensitive polymer) and developed to form 3D images on the substrate.

Lithography process: substrate preparation, photoresist spin coat, prebake exposure, postexposure bake, development, postbake, resist strip

Substrate Preparation improves adhesion of photoresist material to substrate by cleaning, baking at 600 C or using chemicals to get rid of water, and adding an adhesion promotor.

Photoresist Coating. Spin coating: the photoresist is made liquid, poured on, then spun on a turntable at high speed. This has to be very carefully controlled to get the right thickness and uniformity which varies depending on the substrate material.

Postapply Bake: Dry the photoresist after the spin coat process by removing excess solvent using a hot, high-mass metal plate in a vacuum

Alignment & Exposure: Scanning projection printing uses a slit of light from the mask onto the wafer after it’s been aligned properly (very complicated)

Postexposure bake: To remove standing wave ridges

Development: Once exposed, the photoresist must be developed with tetramethyl ammonium hydroxide poured on a rotating wafer or sprayed on

Ion Implantation

Dozens of ion implantation steps are usually required that very precisely plant the right amount of dopants (ions) at just the right spot. p-tpye dopant boron (B+, FB2_,), n-type phosphorus, arsenic, other dpoants are indium, antimony, germanium etc

Beamline architectures: 3 types of tools all have implanter beamlines that start with an ion source and extraction optics that inject an appropriately shaped beam of ions into subsequent elements of the beamline. Implanter beamlines also need a mass analysis devise to provide momentum dispersion and transverse focusing of the ion beams. There are high-current beamlines, high-energy beamlines, and medium current beamlines.

Multi-wafer & single wafer. High-current and energy architectures use a multi-wafer batch processing chamber where many wafers can be implanted at once using a spinning disk at 1000 rpm of the wafers across a fixed-spot beam. Single wafer processing just ipmlants a single wafer.

Thermal Annealing: Postimplant thermal annealing repairs the crystalline structure of the wafer from the damage created during implantation and electrical activation of the new dopant ions. This is done usually with isothermal lamp or hot-walled furnaces

Wet Etching: The etch process transfers a pattern from a mask layer to the underlying layer by using a chemical etchant, and the rest is intact because it’s protected by the mask layer below. Wet chemical etching reacts with the substrate to produce soluble products that can be washed off. Dry etching uses plasma gas to etch both chemically and physically.

- HF-based etching chemistry Hydrofluoric acid (HF)-based etching are the most commonly used wet etchants.

- Metal Etching Used on aluminum (al), copper, gold, nickel, platinum, chromium, and titanium. cyanide solutions, phosphoric acid, ammonia

- Wet etching for compound semiconductor: Oxidize substrate surface and remove soluble reaction products.

Wet Etching Equipment: Immersion processors (wet benches). Wafers are immersed, then rinsed, often with physical agitation from ultrasonic agitation, nitrogen bubbling through the solution, or mechanically. Rinse tanks : 1) quick-dump with top spray, 2) cascade overflow with hot water, 3) Spin rinse dry. Drying equipment: 1) hot nitrogen, vacuum, slow pull, or isopropyl alcohol vapor drying

Environmental and health issues: Some of the most hazardous chemicals are used in the wet etching process, such as hydrogen peroxides. Strong acids and oxidizers are often mixed and heated generating fumes that can spread highly corrosive droplets. Cynaide solutions for gold can turn into the deadly gas HCN.

Plasma Etching. Plasma is the only way to etch micron-sized features and faithfully transfer submicron patterns and has replaced wet etching in making semiconductors. The 4 basic ways plasma etching is used are: 1) sputtering ions strike the substrate and eject materials at low pressure, 2) chemical etching where neutrals in the plasma react with substrate materials to form volatile products, 3) ion-enhanced etching where ions strike the substrate surface, enhance chemical reactivity, and improve desorption of volatile products, 4) sidewall inhibitor etching

Plasma etching systems: This equipment varies depending on what frequencies, pressures, external power sources, load size, and vicinity of the substrate to the plasma source is desired.

Silicon etching: done with F-, Cl-, and Br-based chemistries using ion-driven anisotropy or inhibitor-assisted anisotropy.

Dielectric materials and metal etching: Other materials besides silicon need to be etched when making IC devices.

MEMS device plasma etching: Microelectromechanical systems device makers don’t use transistors as the basic building blocks like IC devices, nor are the relatively uniform. MEMS can be tens to hundreds of micrometers deep.

Multiplex etching: Time Division Multiplex etching alternates plasma deposition with etching steps.

Chapter 38 the fabrication plant.

I am going to skip ahead to give you an idea of what the building is like where all these processes are going on.

The temperature must stay between 68.4 and 71.4 degrees Fahrenheit, and the relative humidity between 44.1% and 45.9% or the equipment doesn’t function properly. It becomes misaligned, impacts repeatability of the developed process, and reduces output. This is a huge building to keep within such a narrow range, and some areas require even narrower ranges of between 69.9 and 70.1, which increases costs up to 50%.

Table 38.5 Generic cleanroom ISO class 3 criteria specifications.

- Air change rate. 600 times per hour

- Airflow. Unidirectional

- Air filtration. Terminal (UPLA) filters 99.99995% efficience at .012 um

- Air handlers. Rooftop makeup AHUs, recirculating indoor units

- Air pressure. Pressure differential + .005” w.g. versus reference corridor

- Temperature. 70 degrees Fahrenheit +/- 2%, no more than 3% variation in 4 hours

- Humidity. 45% relative humidity +/ 1/2%, no more than 3% variation in 4 hours

- Exhausts. Scrubbed acid, abated solvents, general, and heat exhausts

- Vibration and noise. NC-50, < 300 uin/s peak to peak, 0-15 Hz

- Magnetic flux. .5 G maximum

- Electrostatic charge. 1 mJ x 10-7 m2 maximum

- Energy. 1,200,000 BTU per square foot per year (operating 23 hours a day, 365 days)

- Form, function. 60,000 ft2 floor. Bay and chase, subbasement, mec. Floor, office

- Particulate. Particles per cubic food, .3 u in size <1 .12 u in size < 35

- Process piping. DI water-virgin PVDF, ultrapure gases, ultrapure chemicals-seamless 316L electropolished tubing stainless steel

Mechanical only construction:

- makeup AHUs with ductwork

- recirculating AHUs

- cooling: refrigerant coir. Air cooled with piping

- Heating: steam. Zone reheat-electric

- Humidification: steam with piping

- Exhaust systems with ductwork

- Process piping

- Fan-filter units with grid

- Cooling: chillers with cooling towers

- Heating: hot water. Zone reheat-hot water

- Humidification: adiabatic

Section titles of the clean room design and construction chapter:

- Airflow Layouts and Patterns: unidirectional airflow, turbulent airflow, air changes. Recirculating air units. Controls. Electrical. Structural. Air-balancing dampers. Return-air path. Differentuial-pressurization limitations.

- Ceiling systems, wall systems, floor systems. Structure. Fire sprinkler penetrations. HEPA ceiling coverage. Unidirectional flow ceiling height. Unidirectional flow ceiling grid alignment.

- Cleanroom Lighting. Lighting type, levels, yellow lighting

- Cleanroom walls, windows, doors and flooring. Interior movable walls construction. Rearrangement flexibility. Finish. Doors. Caulking practice. Clean flooring. Antistatic flooring. Floor finish. Floor installation. Vibration-sensitive tool mounting.

- Exhaust systems, makeup air systems, recirculation air systems

- Air Pressure differential.

- Process Contamination Control. Air filtration, prevention, isolation, sweep

- Vibration and noise control. Concrete “waffle” slabs under the cleanroom floor

- Magnetic and electromagnetic flux.

- Electrostatic charge of air and surfaces.

- Life Safety.

There are thousands of companies involved in clean room technologies

http://www.cemag.us/companies

Uncle!

At this point I am only 20% of the way through this 800-page book. I can’t take it anymore! I’ve checked it out twice and must return it, and if I check it out again, and again, and again to finish this post, I’ll wonder whatever happened to my life, it will almost be over…

So below is an outline of some of the chapters I didn’t cover on manufacturing, and then you’ll just have to get the book to see the other dozens of missing chapters.

Chapter 12. Etching of GaAs and Related Materials

- Front Etch of GaAs

- Backside Etch of GaAs

- Etching of InP Materials

- Etching of GaN Materials

- ENDPOINT DETECTION IN PLASMA ETCHING

- Pressure change, Bias change, Mass spectrometry, laser interferometry and reflectance, optical emission spectroscopy

Chapter 13: Physical Vapor Deposition

- VACUUM EVAPORATION

- Evaporator equipment: resistive heater or electron beam

- LAYERS DEPOSITED USING EVAPORATOIN AND THEIR PROPERTIES

- Metals, alloys, multilayer, chemical compounds, reactive evaporation

- SPUTTERING

- Stage 1: creation of ions through collision of inert gas atoms (Ar) with electrons and acceleration of ions toward a target, Stage 2: removing of target atoms by impact of ions with target, Stage 3: transport of free target atoms to the substrate, Stage 4: Condensation of target atoms on the substrate

- Mechanism

- Film Microstructure and Mechanical Properties

- SPUTTER EQUIPMENT: DC-sputtering, HF/RF sputtering

- Vacuum system, cooling water, Cathodes and Targets

- Self-bias Effect

- Bias Sputtering

- Reactive Sputtering

- Magnetron Sputtering

- LAYERS DEPOSITED USING SPUTTERING

- Metals: Au, Pt, Pd, Ni, Ti, Al, Cr, Mo

- Alloys: NiCr, CrSi, TiW

- Multilayers: Cr-Al, Ti-Au, Ti-Pd-Au, Ti-TiN-Au, Ti-TiWN-Au, NiCr-Ni-Au, SnO2, Cr-Al

- Chemical compounds: Al2O3, SnO2, SiO2, ZnO, Ga2O3, HfB2, NiO, V2O5, Mo2O3, In2O3, glass (pyrex)

- Step Coverage

Chapter 14: Chemical Vapor Deposition (CVD)

In this step, reactive gases pass over the silicon wafer and are adsorbed onto the surface where the reaction forms a film. By-products leave as gases and pumped away. Reactions are activated heating or radio frequency energy through plasma.

Components/Equipment:

- Chamber

- Pumps

- Wafer Handling

- Gas Delivery System

- Radio Frequency system

PRECOATING AND CLEANING with fluorine containing molecules such as NF3, CF4, and C2F6, which react with the cvd film deposited on the chamber walls and forms volatile compounds that are then pumped away.

TROUBLESHOOTING particle problems: Gas-phase nucleation, Flaking, Abrasion, Condensation.

Deposition rate and Uniformity.

Chapter 15: Epitaxy

- Epitaxy refers to the growth of a crystal on top of a host crystal in an orderly way. The three most common modes are 1) layer-by-layer growth 2) Nucleation Growth 3) layer-by-layer followed by nucleation growth

- Growth techniques and equipment

- Molecular Beam Epitaxy

- Silicon Epitaxy for Advanced CMOS technology: overview of Silicon Epitaxy

- Epitaxy Parametric

- Thickness. Resistivity. Surface defects. Bulk Metals. Flatness and Nanotopography.

Chapter 16: ECD Fundamentals

- Basic Process Flow for Copper Damascene Processing,

- Fundamental ECD technology (how plating works).

- Basic electrochemistry.

Chapter 17: Chemical Mechanical Polishing.

- Most common CMP processes: Oxide/Poly Si CMP, Metal CMP,

- Removal Rate control.

- Within Wafer Uniformity Control

- Process consumables

- Pad conditioning

- Endpoint systems

- In Situ metrology

- Post-CMP Wafer Cleaning

- Dry in-Wet out CMP tools, Dry in-Dry out tool, CMP wafer cleaners, Internal CMP cleaning systems

- Common CMP platforms & tools: single head rotational systems, multihead rotational CMP systems, Multiplaten CMP systems, Orbital CMP systems, Linear Drive CMP tools

- CMP Process Waste Management: oxide CMP process waste, Metal CMP process waste

Chapter 18: Wet Cleaning

- Contaminants.

- Theory of Particle Adhesion.

- Wet Processing techniques: 1) liquid chemical cleaning, 2) scrubbing, 3) Pressurized Jet Cleaning, 4) Sonic Cleaning

- Wet Cleaning Equipment: immersion, placing the wafers in a tank filled with a chemical, spray, using a nozzle to spray the wafers with a chemical, and dispense, directing a stream of appropriate chemical to the wafer

- Front End-of-Line processes: Wafer cleans. Post-dry Etch or Ash residue removal. Metal removal. Post-CMP clean. Backside Cleans.

- Back End-of-Line cleaning. Post-CMP. Post-etch residue removal. Backside and bevel cleans.

- Wet Cleaning Equipment technology.

- Batch Tank. Batch Spray. Single Wafer.

Table 41.1 Chemical substances common in Semiconductor manufacturing

Toxic: Ammonia, arsine, boron trifluoride, carbon tetrafluoride, chlorine, hydrochloric acid, hydrofluoric acid, methyl alcohol, nitric acid, methylene chloride, phosphine, phosphorus pentafluoride, 1,1,1-trichloroethane

Corrosive: Acetic acid, ammonia, chlorine, fluorine, hydrochloric acid, hydrofluoric acid, nitric acid, ozone, sulfur dioxide, sulfuric acid

Irritants: Acetic acid, acetone, ammonia, chlorine, formaldehyde, isoproponal, methyl alcohol, NMP, Ozone,, PGME, PGMEA, Tolulene, Xylene

Odorous: acetic acid, ammonia, butyl acetate, chlorine, formaldehyde, hydrofluoric acid, hydrogen sulfide, isopropanol, NMP, PGME, PGMEA, phosphine, xylene

References

Andrews, Esther. Jan 22, 2012. What’s Behind the Products you Love? intel.com

Benini, Luca. Resource Allocation & Scheduling in Moore’s Law Twilight Zone. Università di Bologna & STMicroelectronics

Fiddler, Jerry (chairman of Wind River Systems). 2002 “Keynoter says chip value is in its intellectual property,” EE Times

Mims, C. April 20, 2010. The High Cost of Upholding Moore’s Law. Technology Review.

Nuttall, Chris. July 20, 2009. “Moore’s Law reaches its economic limits”, Financial Times.

Reuters (2019) Samsung electronics chip output at South Korea plant partly halted due to short blackout. https://www.reuters.com/article/us-samsung-elec-plant/samsung-electronics-chip-output-at-south-korea-plant-partly-halted-due-to-short-blackout-idUSKBN1Z01K3

SeekingAlpha (2014) ASML And Smaller Computer Chips: Will Moore’s Law Break?

Ting-Fang C, Li L (2021) Taiwan’s chip industry under threat as drought turns critical. TSMC and UMC activate water-supply plans as reservoirs face depletion in 60 days. Nikkei Asia.

16 Responses to How are microchips made?